Part of conventional CAD layout navigation in failure analysis work involves identifying defect regions and overlaying the physical image from the microscopes to a CAD database that links the design layout and its logical circuit schematic, along with net list navigation. Current manual alignment by feature points is inaccurate, slow and error-prone. With design layouts becoming increasingly more complex, this difficulty poses challenges to the productivity of failure analysis labs’ workflows.

Our first product, ImageMapper, solves this problem by enabling fully-automatic search and alignment of inspection images to IC design layouts. ImageMapper is a plugin to Synopsys Camelot.

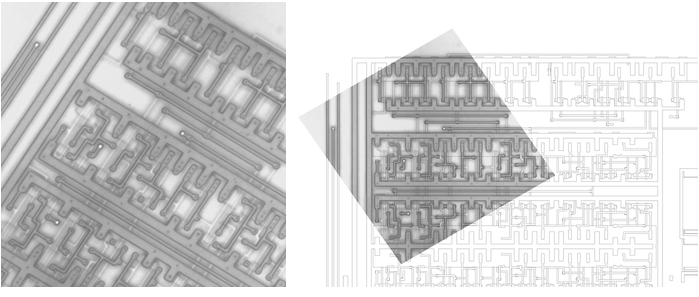

| The key features of ImageMapper are: • Automatically matches and aligns die image to design layout. • Aligns images of unknown scale, translation, rotation, and skew. • Handles a wide range of image magnification. • Works with images that show multiple layers of the chip. • Supports SEM, FIB, and Optical Microscope images. • Detects repeated patterns. • Is robust to fabrication defects and image noise. ImageMapper is valuable to users in many ways: Below are some examples to demonstrate ImageMapper’s capabilities:

|